なぜAIワークロードは「Von Neumann型アーキテクチャ」の限界を顕在化させるのか

長年にわたり、Von Neumann型アーキテクチャはコンピューティングの基本構造として機能してきました。

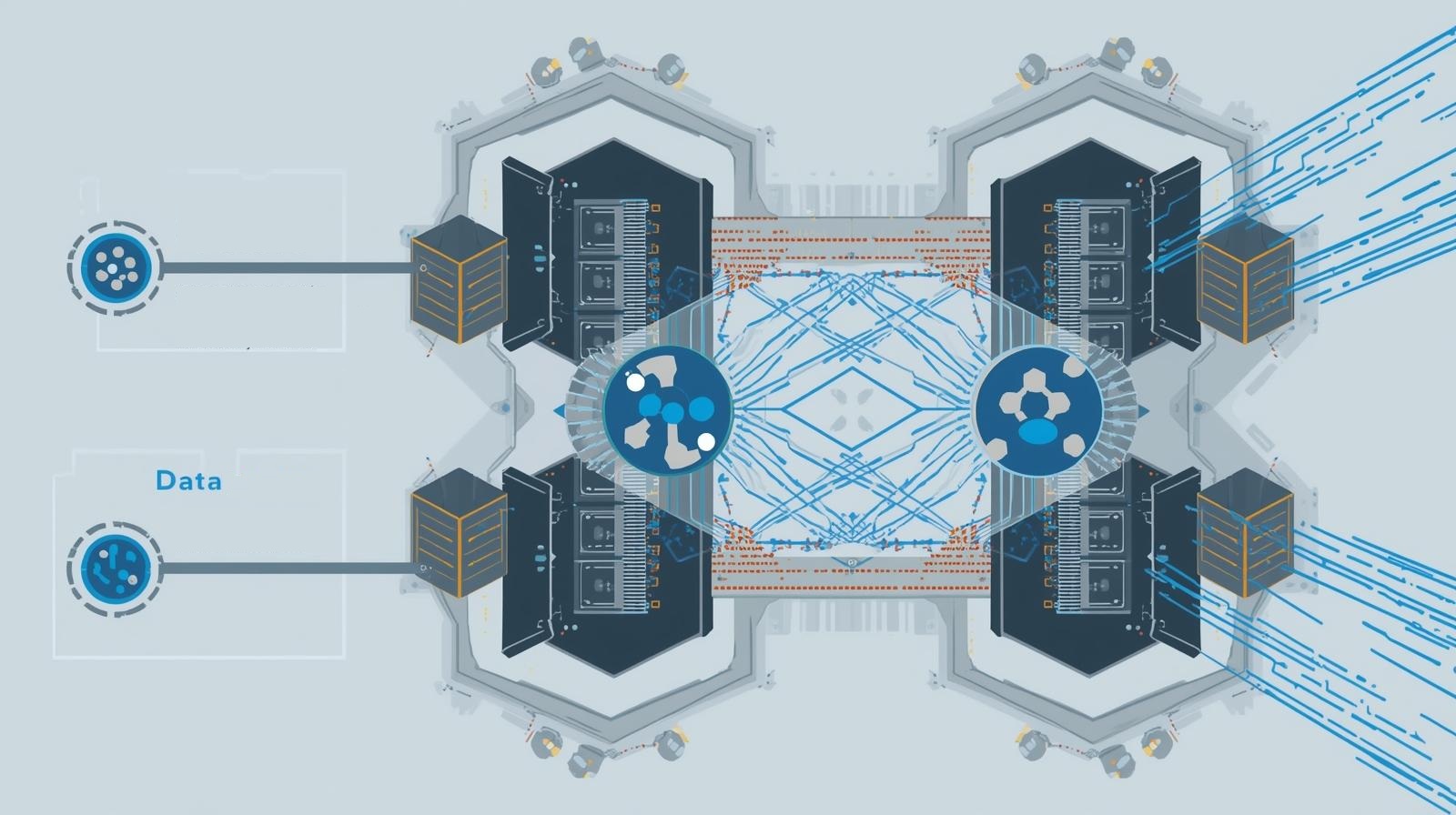

CPUやGPU、メモリを明確に分離し、バスを介してデータをやり取りするこのモデルは、多くの用途において有効でした。

しかしAIやHPCのような大規模データ処理ワークロードでは、この前提が制約として顕在化しつつあります。 本コラムでは、その背景を「データ移動」という観点から整理します。

ボトルネックは「演算」ではなく「データ移動」

近年のAIインフラでは、演算性能そのものは急速に向上しています。

一方で、CPUやGPUが待たされる時間の多くは、計算ではなくデータの受け渡しに起因するケースが増えています。

- メモリからデータを取得する

- 計算後に結果を書き戻す

- 次の処理のために再び転送する

この繰り返しが積み重なることで、システム全体の効率が制限される場合があります。

Von Neumannボトルネックとは

Von Neumannボトルネックとは、コンピュートとメモリが分離されている構造により、 データ転送が性能の上限を決めてしまう現象を指します。

AIワークロードでは、モデルの大型化やデータ参照の増加により、 メモリアクセスが頻繁に発生しやすく、ボトルネックがより顕著に見えることがあります。

なぜスケールすると影響が大きくなるのか

ノードやアクセラレータを増やすことで、演算性能は理論上スケールします。

しかし、データ移動の経路や帯域が同じ比率で拡張されない場合、次のような現象が起こり得ます。

- GPUのアイドル時間が増える

- 利用率が低下する

- 消費電力あたりの効率が下がる

これは単体性能の問題というより、構成や前提条件(データ移動の設計)に起因するケースが多い点が重要です。

Processing Near Memoryという考え方

こうした背景から、処理をデータに近づけるという発想が注目されるようになっています。

Processing Near Memory(PNM)は、データ移動量を抑える観点で議論されるアプローチの一つです。

- データ移動量の削減を狙う

- レイテンシの影響を受けにくい設計を検討する

- メモリ集約型処理に適した構造を考える

ここで重要なのは、PNMが単一の実装方式ではなく、アーキテクチャ設計上の方向性として検討される点です。 評価ではワークロード特性やソフトウェアスタックとの整合も前提になります。

おわりに

Von Neumann型アーキテクチャは今後も多くの用途で重要な役割を果たし続けます。

一方で、AIやHPCのようなワークロードでは、その前提を補完・拡張する設計が求められ始めています。

次回は、こうした構造的な制約が具体的なワークロード(例:RAGなど)でどのように表面化するのかを整理します。

筆者について

I.J.ビジネス道社は、日本企業向けにイスラエル発技術との協業検討を実務ベースで支援しています。

本コラムは特定製品の紹介を目的とするものではなく、AI/HPC領域で起きやすい論点の整理として作成しています。

技術検討の前提整理(課題の構造化、検討観点の整理)が必要な場合は、お問い合わせフォームよりご連絡ください。